# 저유전체 고분자 접착 물질을 이용한 웨이퍼 본딩을 포함하는 웨이퍼 레벨 3차원 집적회로 구현에 관한 연구

권용재<sup>†</sup>· 석종원\* · Jian-Qiang Lu\*\* · Timothy Cale\*\* · Ronald Gutmann\*\*

인하공업전문대학교 화공환경과 402-752 인천시 남구 용현동 253 \*중앙대학교 기계공학부 156-756 서울시 동작구 흑석동 221 \*\*포커스 센터-뉴욕 렌슬리어 미국 뉴욕주 12180 트로이시 렌슬리어 폴리테크닉 인스티튜트 (2007년 2월 5일 접수, 2007년 5월 9일 채택)

## A Study on Wafer-Level 3D Integration Including Wafer Bonding using Low-k Polymeric Adhesive

Yongchai Kwon<sup>†</sup>, Jongwon Seok\*, Jian-Qiang Lu\*\*, Timothy Cale\*\* and Ronald Gutmann\*\*

Department of Chemical and Environmental Technology, Inha Technical College, 253, Yonghyun-dong, Nam-gu, Incheon 402-752, Korea \*School of Mechanical Engineering, College of Engineering, Chung-Ang University, 221, Heukseok-dong, Dongjak-gu, Seoul 156-756, Korea

\*\*Focus Center - New York, Rensselaer: Interconnections for Hyperintegration, Rensselaer Polytechnic Institute, Troy NY 12180-3590 USA

(Received 5 February 2007; accepted 9 May 2007)

### 요 약

웨이퍼 레벨(WL) 3차원(3D) 집적을 구현하기 위해 저유전체 고분자를 본당 접착제로 이용한 웨이퍼 본당과, 적충된 웨이퍼간 전기배선 형성을 위해 구리 다마신(damascene) 공정을 사용하는 방법을 소개한다. 이러한 방법을 이용하여 웨이퍼 레벨 3차원 칩의 특성 평가를 위해 적충된 웨이퍼간 3차원 비아(via) 고리 구조를 제작하고, 그 구조의 기계적, 전기적 특성을 연속적으로 연결된 서로 다른 크기의 비아를 통해 평가하였다. 또한, 웨이퍼간 적충을 위해 필수적인 저유전체 고분자 수지를 이용한 웨이퍼 본당 공정의 다음과 같은 특성 평가를 수행하였다. (1) 광학 검사에 의한 본당된 영역의 정도 평가, (2) 면도날(razor blade) 시험에 의한 본당된 웨이퍼들의 정성적인 본당 결합력 평가, (3) 4·점 급힘시험(four point bending test)에 의한 본당된 웨이퍼들의 정량적인 본당 결합력 평가. 본 연구를 위해 4가지의 서로 다른 저유전체 고분자인 benzocyclobutene(BCB), Flare, methylsilsesquioxane(MSSQ) 그리고 parylene-N을 선정하여 웨이퍼 본당용 수지에 대한 적합성을 검토하였고, 상기 평가 과정을 거쳐 BCB와 Flare를 1차적인 본당용 수지로 선정하였다. 한편 BCB와 Flare를 비교해 본 결과, Flare를 이용하여 본당된 웨이퍼들이 BCB를 이용하여 본당된 웨이퍼보다 더 높은 본당 결합력을 보여주지만, BCB를 이용해 본당된 웨이퍼들은 여전히 칩 back-end-of-the-line (BEOL) 공정조건에 부합되는 본당 결합력을 가지는 동시에 동공이 거의 없는 100%에 가까운 본당 영역을 재현성있게 보여주기 때문에 본 연구에서는 BCB가 본당용 수지로 더 적합하다고 판단하였다.

Abstract – A technology platform for wafer-level three-dimensional integration circuits (3D-ICs) is presented, and that uses wafer bonding with low-k polymeric adhesives and Cu damascene inter-wafer interconnects. In this work, one of such technical platforms is explained and characterized using a test vehicle of inter-wafer 3D via-chain structures. Electrical and mechanical characterizations of the structure are performed using continuously connected 3D via-chains. Evaluation results of the wafer bonding, which is a necessary process for stacking the wafers and uses low-k dielectrics as polymeric adhesive, are also presented through the wafer bonding between a glass wafer and a silicon wafer. After wafer bonding, three evaluations are conducted; (1) the fraction of bonded area is measured through the optical inspection, (2) the qualitative bond strength test to inspect the separation of the bonded wafers is taken by a razor blade, and (3) the quantitative bond strength is measured by a four point bending. To date, benzocyclobutene (BCB), Flare<sup>TM</sup>, methylsilsesquioxane (MSSQ) and parylene-N were considered as bonding adhesives. Of the candidates, BCB and Flare<sup>TM</sup>

E-mail: kwony@inhatc.ac.kr

<sup>&</sup>lt;sup>†</sup>To whom correspondence should be addressed.

were determined as adhesives after screening tests. By comparing BCB and Flare<sup>TM</sup>, it was deduced that BCB is better as a baseline adhesive. It was because although wafer pairs bonded using Flare<sup>TM</sup> has a higher bond strength than those using BCB, wafer pairs bonded using BCB is still higher than that at the interface between Cu and porous low-k interlevel dielectrics (ILD), indicating almost 100% of bonded area routinely.

Key words: Three-dimensional Integration Circuits, Cu Damascene, Wafer Bonding, Low-k Polymeric Adhesive, Bond Strength

#### 1. 서 론

근래에 들어 시스템온칩(system-on-a-chip; SoC) 제품들이 수평적 상보성 금속산화물 반도체(complementary metal oxide semiconductor; CMOS) 2차원 집적 회로(2D ICs)를 기반으로 하여 개발되고 있다. 그러한 SoC 제품들은 단일하게 패키징된 집적 회로에 비해 높은 성능, 낮은 전력소비, 높은 대역폭(bandwidth)뿐 아니라, 잡음 여유도 (noise immunity), 칩 디자인의 유연성, 그리고 패키지 비용 등에 있어 많은 장점들을 가진다[1]. 그러나, 일반적인 CMOS에 기반을 둔실리콘 웨이퍼에 이러한 기술들을 저비용으로 개발해 접목하는 것은 매우 어렵다. 고성능을 가진 SoC 제품들에 대한 요구와 틈새 제품들(niche applications)의 디자인에서의 유연성이 증가하면서, 반도체 업체들은 제조 공정시 사용되는 물질이나 공정 자체의 제한점을 완화하기 위한 대안적 해법들을 고려하고 있다[2].

이러한 해법중의 하나는 IC 웨이퍼들을 수직적으로 적층하는 웨 이퍼 레벨(WL) 3차원(3D) 집적이다[3-7]. 즉, 이는 최적화된 단위 공정들을 이용하여 제조한 IC 웨이퍼들(logic, memory 웨이퍼 등) 을 웨이퍼 간 정렬(align)과 본딩, 연삭 및 연마, 수직 전기배선 형 성 과정을 거쳐 'SoC'의 형태로서 구체화 시키는 공정이다. 이러한 기술을 사용하면 다른 기능들을 가지는 IC 웨이퍼들 간의 3차원 집 적이 가능하다. 초기에 주목을 받은 응용 분야는 마이크로 프로세 서(microprocessors), 특용도 IC(application specific ICs; ASICs) 등 이었으나 최근에는 무선고주파(radio frequency; RF), 아날로그 광 소자(analog, optical devices), 그리고 미세 전자기계 시스템(microelectro-mechanical systems; MEMS) 분야들로 확장되고 있다. 또한, 최근에는 이러한 이종 웨이퍼간 집적에 대한 수요뿐 아니라 시스템 성능을 극대화 하기 위해 웨이퍼 레벨에서의 전기 배선(global interconnect)간의 신호 지연을 줄이는 것이 중요한 문제로 대두되고 있다. 따라서, 최소화 시켜야 하는 단위 노드(node)의 크기는 빠르 게 변화하고, 대안으로 생각했던 구리/저유전체 집적 구조를 구현하 는 것은 예상보다 오랜 시간이 걸릴 것으로 예측되기 때문에, 전기 배선들의 신호지연을 감소시킬 새로운 방법이 필요하다[1,2]. 이러 한 새로운 시도의 하나로 전기회로를 수직적 3차원 회로로 집적하 는 것이 대두되었다. 이를 수평적 2차원 회로 구조와 비교했을 때, 신호지연이 약 60% 감소되는 것으로 예측되었다[2].

과거 수년 동안, 긴 전기배선의 길이를 줄이고자 하는 웨이퍼 레벨 3차원 회로 집적에 대한 개념은 집적 회로의 성능 향상을 위해 제안되었다[2-7]. 그 개념을 달성하려는 기술로서 내장형 박막 트랜지스터(embedded thin film transistors, TFTs)나 웨이퍼 본딩을 이용해 웨이퍼들을 적충한 후 그 웨이퍼들을 내부적으로 연결시키기 위해 비아를 이용하는 방법이 주로 고려되었다[6]. 한편, 본딩 매개체로서 금속[5, 7]이나 저유전체 고분자 수지[3, 4]를 이용하는 웨이퍼본딩 기술들이 웨이퍼간 전기 배선 연결을 위해 수 마이크론 크기의 비아를 형성하는 기술과 더불어 개발되고 있다.

본 논문에서, 웨이퍼 레벨 3차원 회로 집적을 위한 한가지 접근 방법(3차원 비아 고리 구조)과 더불어 각 단위 공정 개발 및 전기적 특성 시험 결과(비아 고리 구조의 저항값)를 소개하고, 이러한 단위 공정 중에서, 저유전체 고분자를 본당용 수지로 이용한 실리콘과 유리 웨이퍼 사이의 본당에 필요한[8,9] 특성 평가 결과를 논의하고 자한다. 본 연구에서는 본당용 수지로서 benzocyclobutene(BCB), poly arylene ether(PAE) 계열인 Flare<sup>tm</sup>, methylsilsesquioxane(MSSQ) 그리고 parylene-N을 고려하였다. 먼저, 이러한 네가지 고분자 수지들로 본당된 웨이퍼들에 대해 광학 검사에 의한 초기 예비검사 (screening test)와 면도날(razor blade)을 이용한 정성적인 본당 결합력시험을 진행하였다. 이러한 시험 과정을 거쳐 BCB와 Flare의 두가지 고분자 수지를 본당용 수지로 일차 선정하였으며, 각각의 고분자 수지로 본당된 웨이퍼들의 정량적인 본당 결합력은 4~점 급힘시험(four point bending test)을 이용하여 평가 하였다.

## 2. 실 험

#### 2-1. 2차원 비아 고리 구조의 제작 공정

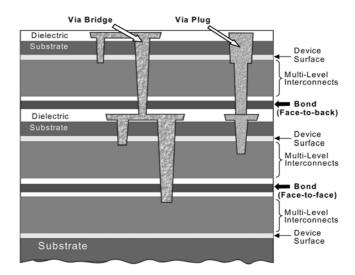

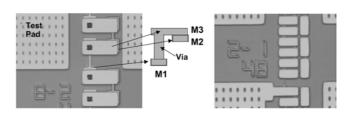

Fig. 1은 웨이퍼 레벨 3차원 집적에 대해 본 연구에서 제안한 접 근 방식을 기초로 한 시편의 구조를 보여준다[3, 10-11]. 이 접근 방식에서 다층 전기 배선들에 의해 패턴이 이미 형성된 웨이퍼들을 정렬(align)한 후 저유전체 고분자 수지와 본딩하고, 이어 웨이퍼 이 면을 연삭(grinding), 연마(polishing) 및 습식 식각법을 이용하여 10 μm 미만까지 얇게 만든다. 또한 높은 종횡비를 갖는 비아의 제작, 구리 및 장벽(barrier) 금속층의 증착 및 화학-기계 연마(chemical mechanical polishing; CMP)를 포함한 구리 다마신 패턴 공정을 이용하여 웨이 퍼간 전기 배선을 형성한다. 2차원으로 집적된 칩에서 수 mm의 길

Fig. 1. 3D integration concept using wafer-bonding, showing dielectric adhesive bonding interface, vertical vias (plug- and bridge-type), and bonding approaches of "face-to-face" and "face-to-back".

Korean Chem. Eng. Res., Vol. 45, No. 5, October, 2007

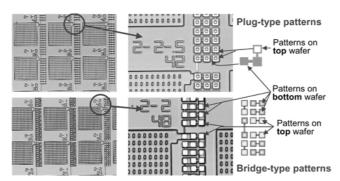

Fig. 2. 200 mm wafer-to-wafer alignment accuracy with via-chain test structures, indicating  $1\sim2$   $\mu m$  alignment can be achieved.

이를 갖는 긴 전기 배선들은 이러한 과정을 거쳐 3차원으로 집적된 칩에서 수  $\mu$ m의 수직한 비아에 의해 연결되는 구조로 대체된다.

이러한 접근 방식은 다른 웨이퍼 적층 방법들과 비교할 때 3가지 주된 장점들을 가지고 있다[3]. 즉, (1) 웨이퍼 레벨에서 발생하는 웨이퍼의 휨(bow) 현상을 수용할 수 있으며, (2) 핸들링 웨이퍼가 필요하지 않아서 비용과 공정의 단순성 측면에서 유리하며, (3) 단위 공정들의 변화없이 3개 혹은 더 많은 웨이퍼들을 적층할 수 있다. 이 방법에 의해 웨이퍼간 전기 배선의 밀도를 극대화 할 수 있다. 예를 들면,  $10~\mu m$  간격으로  $2~\mu m$  지름을 가지는 비아들의 경우 단지 3%의 실리콘 영역을 이용하여 단위  $mm^2$  당  $5\times10^5$ 개의 브릿지(bridge)형 비아를 생성할 수 있다[6].

Fig. 2는 비아의 식각 공정을 수행하기 전에 다양한 패드 및 플러그 크기,  $2 \mu m$  비아에 대한 브릿지 형과 플러그 형의 비아 고리 구조들 및 구리 다마신을 이용하여 공정을 진행한 웨이퍼들을 보여준다. 이 웨이퍼들은 각각 이미 확립된 표준 공정을 통해 정렬, 본딩, 박층화, 재배선 패턴닝, 플러그 패드 패턴닝 그리고 테스트 패드 패턴닝 공정을 거쳤으며 대략적으로  $1\sim2 \mu m$ 의 벗어난 정도를 가진 정렬 결과를 EVG smartview aligner를 이용하여 얻었다.

각 웨이퍼들 간의 수직 전기 배선 형성을 위해서는 대략 10 μm 정도 깊이의 비아를 식각하여야 한다. 본 논문에서는, 0.2 μm 두께의 크롬(Cr)을 깊은 비아 식각을 위한 마스크로 이용하였으며 적층 구조에 포함된 다양한 물질들을 식각하기 위해 ICP(inductively coupled plasma) 방식을 사용하였다. 식각 후 차례로 비아제거 작업을 거쳐 저온(<300°C)에서 TaN 장벽층(barrier layer)과 화학 증착(CVD) 법을 이용한 구리 충진 공정을 진행한 후, 최종적으로 CMP 공정을 수행하였다[10].

#### 2-2. 웨이퍼 본딩 및 본딩 결합력 평가

고분자 수지들(BCB, Flarel<sup>III</sup>, MSSQ 및 parylene-N)을 웨이퍼위에 코팅하기 전에, 패턴이 없는 실리콘과 유리 웨이퍼들을 화학적으로 클리닝 하였다. 각 웨이퍼들을 2대 1의 wt% 비의 황산( $H_2SO_4$ )과 과수( $H_2O_2$ )용액에 20분간 담가서 클리닝 한 후, 고분자 수지를 코팅하였다. 스핀 도포형(BCB, Flare, MSSQ)의 경우, 코팅과 베이킹은 FlexiFab spin coate를 이용하여 수행하였다. 한편, BCB (cyclotene 3022-35)의 경우, 코팅전에 본딩 결합력을 향상시키기 위해 본딩 촉진제(adhesion promoter, AP 3000)를 먼저 코팅하였다. 코팅된 웨이퍼들은 BCB에 포함된 용제를 제거하기 위해 170  $^{\circ}$ C에서 2분 동안 베이킹 하였다. 그런 다음, 코팅된 BCB를 ellipsometry

를 이용하여 측정한 후 평균 1.3 μm 두께로 200 mm 웨이퍼에 일 정하게 재코팅하였다(2% 미만의 표준 편차). Flare(Flare 4 k)는 BCB 와 달리, 웨이퍼 위의 매달린(dangling) 본드들과 결합 가능한 정도 의 실라놀(silanol) 기를 가진 것으로 추정되므로, 본딩 촉진제를 이 용하지 않았다. Flare로 코팅된 웨이퍼들을 200, 250, 그리고 300 ℃ 에서 각각 2분 동안 베이킹 한 후, Flare의 두께를 ellipsometry를 이 용하여 측정하고, 평균 0.3 µm 두께로 재코팅 하였다(1% 미만의 표 준 편차). MSSQ(Accuspin T-18)는 Flare 처럼 본딩 촉진제를 이용 하지 않고 코팅 후 160 ℃에서 1.5분 동안 베이킹 하였다. 코팅과 베이킹 후, MSSQ의 두께를 ellipsometry를 이용하여 측정하고, 평 균 0.5 μm의 두께로 재코팅 하였다(2% 미만의 표준 편차). 스핀 도 포형 고분자들과 달리, parylene-N은 증착 공정을 통해 웨이퍼위에 코팅하며, 본딩 결합력을 향상시키기 위해 본딩 촉진제(A-174)를 함 께 코팅하였다. 코팅 후 parylene-N의 두께를 ellipsometry를 이용하 여 측정하고, 평균 1.0 μm 두께로 재코팅하였다(2% 미만의 표준 편 차)[8, 9].

웨이퍼 접촉과 본딩은 EVG EV501 웨이퍼 본더를 이용하여 수 행하였다. 고분자 수지가 코팅된 두 웨이퍼를(상부 및 하부 웨이퍼) 본더 척(chuck)에 위치시키고 우선 EVG EV640 smart-view aligner 에서 정렬 작업을 거친 후 본더로 옮기고 다단계의 본딩 공정을 수 행하였다[9, 11]. 고분자 수지를 이용한 본딩은 크게 (1) 진공, (2) 가 열, (3) 압착, (4) 냉각 의 4가지 공정단계를 포함한다. 본딩 공정을 진행할 때, 본더는 우선 10<sup>-4</sup> mbar까지 진공화 시키고 미리 결정된 최종 본딩 온도까지 가열하였다. 이때, 최종 본딩 온도는 고분자 수 지의 큐어(cure) 온도와 관련 있다. 해당 고분자 수지의 큐어 반응 은 수지 사이 계면에서 가교(crosslinking) 및 상호확산(interdiffusion) 에 의해 이뤄진다. 본 실험에서는 Flare, MSSQ, Parylene-N의 경우 최종 본딩 온도는 400 ℃이고, BCB는 250 ℃로 결정하였다. 이렇 게 결정된 본딩 온도에 도달한 후에는 초기 접촉점을 얻기 위해 상 부 웨이퍼의 중간 지점을 압착하고, 그 후 전체 웨이퍼에 일정한 압 착력을 가하였다. 본딩 온도에서 큐어 반응을 완료하기 위해 필요 한 시간이 지난 후 웨이퍼의 압착 작업을 종료하고, 천천히 냉각하 였다.

고분자 수지를 이용한 본당에서, 압착 단계는 상부 및 하부에 위치한 웨이퍼에 코팅되어 있는 수지 접착층 사이의 간격을 제거해서 원할한 큐어 반응이 일어나게 한다[13]. 그러한 큐어 반응은 두 웨이퍼 사이의 본당 결합력와 본당되는 면적의 정도를 결정하는 중요한 공정이다. 이러한 반응은 3가지의 현상들을 초래하는데, 이들은 (1) 고분자 수지 접착층 사이의 상호확산, (2) 접착층 내의 가교반응, (3) 접착층과 접착제 이웃 층의 매달린 본드들(dangling bonds)과의화학적/물리적 본당이다. 상호확산은 고분자 수지 접착제의 큐어 온도 이상에서 발생된다. 일단 이 온도에 도달하면, 경계면 치유 (interfacial-healing) 반응이 접착층 사이의 계면에서 일어나고, 점차그 계면이 사라지게 된다. 이러한 상호확산이 일어나기 위해서는 접착물질이 무정형 고분자로 구성되어야 한다[13, 14]. 상기 이유로, parylene-N과 같은 반결정질(semi-crystalline) 고분자는 이러한 반응과 이로 인한 경계면 치유 반응이 발생하기 힘들기 때문에 높은 본당 결합력을 가질 수 없다.

본딩 공정 중, 충분히 긴 큐어 시간을 포함한 압착 작업은 BCB의 benzocyclobutene이나, MSSQ의 silanol과 같은 가교 그룹들의 열적 오픈닝을 통해 일어나는 겔화 반응을 초래하여 고분자 수지의 구조

를 경화시킨다. 또한 가교 반응은 고분자 수지의 리플로우(reflow)를 초래한다. 표면에 단차를 가지고 있는 웨이퍼에서 이러한 리플로우는 표면 단차를 동공(void)없이 채우는 데 중요한 역할을 하며,특히 BCB는 이러한 유체적 거동을 보여준다[15]. 화학적 본당의 개념은 주로 접착층과 이웃하는 층의 매달린 본드와의 결합력을 설명하기 위해 사용된다[14]. 화학적 본드들의 형성은 주로 열처리에 의해 일어난다. 특히, 약한 실라놀 기(Si-OH)의 결합을 강한 실록산(siloxane, Si-O-Si) 공유결합으로 바꿔주는 축합반응은 관련된 계면에서 강한 화학적 본당 구조를 형성하기 위해 자주 적용된다[15].

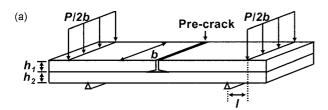

본딩 결합력은 4-점 굽힘시험을 통해 정량적으로 평가하였다. 이 시험법은 Charalambides 등[16]에 의해 제안된 이론에 기초하고 있다. 여기서는 관련된 계면에서의 본딩 결합력을 평가하기 위해 이들이 제안한 공식들을 이용하였다. 4-점 굽힘시험에 사용한 시편들은 우선 본딩 공정이 끝난 웨이퍼들을 (1) 보(beam) 형상으로 커팅하고, (2) 커팅면을 연마 한 후, (3) 프리 크랙의 형성 및 (4) 화학적처리를 거치게 된다[11].

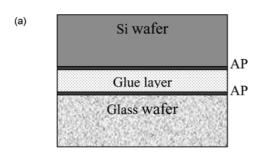

Fig. 3a는 이러한 과정을 거친 보 형상의 시편 구조를 보여준다. 이때 시편은 40 mm의 길이와 4 mm의 폭을 가진다. 특별히 고안된 four-point bending fixture(Zwick T1-FR005TN material testing machine)에 보 시편을 위치 시킨 후, 로드 셀(load cell)을 이용하여 시편에 가해진 하중(load)을 측정하고, 엑추에이터(actuator)를 이용하여 변위 (displacement)를 측정하였다. 하중과 변위 사이의 관계는 10 mm/min의 변위율 단위로 기록하였다. 하중이 보 시편에 가해짐에 따라, 프리 크랙에서 발생하는 굽힘 모멘트는 증가하고, 크랙은 진전된다. 보 시편에서 크랙의 진전을 반영하는 전형적인 하중과 변위의 관계를 Fig. 3b에 도시하였다. 이때 (1) 샘플의 순수 굽힘에 의한 선형 탄성 영역(Fig. 3b의 영역 1), (2) 크랙이 충분히 높은 하중에 의해 약한 계면으로 진입하면서 발생하는 킹크(kink) 균열(Fig. 3b의 영역 2), (3) 그 약한 계면을 따라 균열이 정상상태로 움직이면서 발생하는 평형 하중(load plateau) 영역(Fig. 3b의 영역 3), (4) 평형 하중 영역

Fig. 3. Four-point bending tests: (a) beam specimen geometry for the experiments (b) a typical load-displacement curve for measuring saturation load value.

을 지나, 크랙이 없는 기판의 굽힘에 의해 발생하는 2번째 선형 탄성 영역(Fig. 3b의 영역 4). 보의 굽힘원리를 기초로 계산하면, 본딩 결합력 G.는 다음과 같은 형태로 얻어진다[16].

$$G_c = \frac{3(1 - v_2^2)p_c^2L^2}{2E_2b^2h^3} \left[ \frac{1}{\eta_2^3} - \lambda / \left(\eta_1^3 + \lambda \eta_2^3 + 3\lambda \frac{\eta_1\eta_2}{\eta_1 + \lambda \eta_2}\right) \right]$$

(1)

여기에서  $E_1$ 과  $v_1$ 은 각각 프리 크랙이 있는 웨이퍼의 영률(Young's modulus)과 푸아송 비(Poisson's ratio)이고,  $E_2$ 와  $v_2$ 는 각각 크랙이 없는 웨이퍼의 영률과 푸아송비이다. 또한  $\lambda$ 는  $E_2(1-v_1^2)/E_1(1-v_2^2)$ 으로 표현되는 유효 탄성계수(effective modulus)이고,  $P_c$ 는 평형 하 중값, L은 안쪽과 바깥쪽 핀들 사이의 거리, b는 beam 샘플의 폭, h는 빔 샘플의 전체 두께를 나타낸다. 한편, 여기에서 h는  $h_1+h_2$ 로서 나타낼 수 있으며, 이때,  $h_1$ 은 프리 크랙이 있는 웨이퍼의 두께,  $h_2$ 는 크랙이 없는 웨이퍼의 두께이고  $\eta_i$ 는 상대 두께로써  $\eta_i$ = $h_i$ 0 $(h_1+h_2)(i=1,2)으로 표현된다.$

#### 3. 결과 및 토의

#### 3-1. 비아 고리 테스트 구조의 전기적 특성

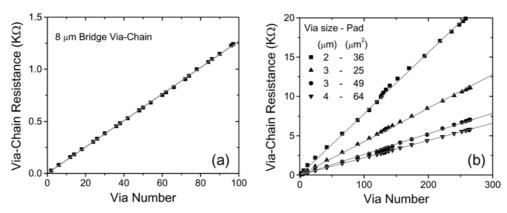

웨이퍼간 비아 고리 시험을 위한 시편은 상기 언급된 단위 공정들을 이용하여 제작하였다. Fig. 4는 브릿지형 비아 고리 구조의 평면사진을 보여준다. Fig. 5는 고리 길이(비아 갯수), 비아 크기 그리고 비아 패드 영역에 따른 브릿지 형 비아 고리 구조의 저항값의 변화를 보여준다. 비록  $\sim$ 5  $\mu\Omega$ -cm²의 비아 고리들의 비접촉 저항 (specific contact resistance)값이 예상치를 상회하지만, 비아 고리 구조의 저항과 고리 길이 사이의 선형 관계는 일정한 3차원 비아 고리 구조가 형성되었음을 입증한다.

### 3-2. 웨이퍼 본딩의 초기 스크리닝 결과

Fig. 6a와 6b는 각각 MSSQ와 parylene-N을 이용하여 본딩을 수행한 웨이퍼들의 본딩 결과를 보여주는 사진이다. 이때 본딩한 기저들(substrates)은 corning 7740 글래스 웨이퍼와 P-type(100) 실리콘 웨이퍼 이다. 상기 두가지 고분자 수지를 이용한 본딩한 결과, 본딩된 영역의 정도가 매우 낮은 것을 광학 검사를 통해 관찰하였고, 정성적인 면도날 시험에서는 고분자 수지들이 이웃면 사이의 계면 혹은 고분자 수지 사이의 계면에서 쉽게 박리되었다. 한편, MSSQ를 이용하여 본당한 웨이퍼들에서는 많은 동공들이 관찰되었다. 이것은 본딩 공정의 접착제가 큐어 되는 동안 발생하는 아래 식 (2)와 같은 축합반응에 의해 생성된 수증기 때문인 것으로 예측된다.

Fig. 4. Top view of the via-chain structure for inter-wafer via sizes of nominal 8 μm (left) and 2 μm (right), showing wafer-to-wafer misalignment of ~1 μm. Metal-1 (M1) is on bottom wafer; metal-2 (M2) is on top wafer. Via and bridge (M3) connect the M1 and M2 to form a via-chain.

Fig. 5. Via-chain resistance vs. via-chain length (via number): (a) for nominal via size of 8  $\mu$ m, (b) for nominal via size of 2, 3, 4  $\mu$ m. The nominal via landing pad is  $12 \times 12 \ \mu\text{m}^2$  for 8  $\mu$ m via chain and others are shown in (b).

$$2 \text{ Si-OH} \rightarrow \text{Si-O-Si} + \text{H}_2\text{O}$$

(2)

상기 반응에 의해 목적 생성물인 실록산 본드들과 함께 생성되는 수증기가 발생하고 본딩 공정 동안 충분히 외부로 유출되지 못하 여 상호 결집에 의해 동공을 형성한다[17].

Parylene-N을 이용한 본딩은 면도날 시험을 통해 쉽게 박리되었다(즉, 이는 결정질 특성에 기인한 낮은 본딩 결합력을 의미한다[13]). Parylene-N 레진이 고분자화 할 때, 그 고분자 고리들은 정형화되므로 움직임이 제한된다. 이렇게 정형화되는 특성은 강한 본딩결합력을 얻기 위해 필요한 가교 반응, 상호 확산(interdiffusion), 그리고 화학 반응들이 일어나기 어렵게 만든다. 또한, parylene-N의 열적 파괴 현상은 그 수지의 본딩 물질로서의 이용을 어렵게 만든다. 자유 라디칼들의 산화 현상은 가장 높이 점유된 분자 궤도에서 하나 적은 전자의 일탈을 초래하고(이것은 주로 탄소-탄소 시그마 본드에서 발생한다) 차례로 탄화수소로 구성된 백본 구조(backbone structure)를 약화시키고 결국 고리들을 절단시킨다. 이 절단된 고리들은 충분히 높은 온도에서 연소 잔류물(char)화, 아웃 가싱(outgas)화하여 동공을 유발하게 된다.

Fig. 6c와 6d는 각각 Flare와 BCB를 이용하여 본당한 웨이퍼들의 사진들이다. MSSQ나 parylene-N을 이용한 본당 결과와 비교했을 때, 훨씬 넓은 본당된 영역이 확보 된 것을 알 수 있다. 따라서, 본 연구에서는 초기 광학 검사에 의한 screen 테스트를 통해 Flare와 BCB를 표준 접착용 고분자 수지 물질로 선정하였다.

### 3-3. Flare와 BCB의 비교

Flare를 접착용 고분자 수지 물질로 이용한 경우, 동공의 수는 MSSQ나 parylene-N을 이용했을 경우 보다 훨씬 적은 것이 입증되었다(Fig. 6c와 Fig. 6a와 6b 비교). Flare는 단단한 특성을 가지는 방향족 혹은 bis-phenol 전구체(precursor)들로 구성되고 이들의 화학적 구조 안에 아웃가성을 유발하는 분자들을 가지고 있지 않기때문에, 남아 있는 용제에 의해 발생될 수 있는 동공을 제외하고는 본딩 공정 동안 반응 부산물이나 축합물에 의한 동공은 거의 발생되지 않는다. 베이킹 후에도 남아있는 용제는 본딩 전에는 상호 얽혀져 있는 고분자 수지안에 놓여 있어 제거되기 힘들다가 큐어 온도 이상에서 레진이 유화되면서 노출되고 아웃가성화 된다. Flare는 또한 이의 방향족 성분에 의한 높은 열 안정성 및 소수성에 기인한내 흡습성을 가진다[18]. 그러나, Flare를 이용해 본딩된 웨이퍼들의

Fig. 6. Wafer bonding results using: (a) MSSQ, (b) Parylene-N, (c) Flare<sup>TM</sup>, (d) BCB. Bonded wafer pair (200 mm) consists of P (100) prime wafer and Corning 7740 glass wafer.

본딩 면적은 넓지만 남아 있는 용제에 의해 발생될 수 있는 동공 때문에, BCB를 이용했을 때 얻어지는 무동공(void-free) 결과에는 도달하지는 못하였다.

BCB를 이용한 본딩은 동공이 없는(void-free) 본딩 결과를 재현성 있게 보여준다. 리플로우에 의해 발생하는 BCB의 'interlocking action'이 이러한 동공이 없는 본딩 결과를 나타내는 주된 이유다 [18, 19]. 즉, BCB의 가교반응 밀도가 다른 비교 물질들에 비해 높고, 상대적으로 더 많은 유동성이 있어서, 큐어 온도 이상에서는 수지의 원할한 움직임에 의해 동공 주위의 빈 공간을 채울 수 있다 (interlocking action). 이러한 interlocking의 증거는 본딩 후, 'edge bead removal(EBR)' 영역에서의 변화로부터 알 수 있다[8, 12]. 스핀 도포 공정에서 웨이퍼 가장자리에 있는 접착 물질은 가장자리비드(edge bead)에 의해 발생하는 동공의 형성을 방지하기 위해 제거하였다. Flare를 이용해 본딩된 웨이퍼들에서 EBR 영역은 웨이퍼

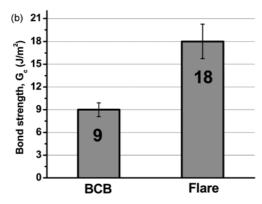

Fig. 7. Experiments for bond strength measurements: (a) geometrical configuration of bonded wafer pair using BCB and Flare<sup>TM</sup> (b) bond strengths of bonded wafer pairs using BCB and Flare<sup>TM</sup> (bond strength of bonded wafers using BCB is 9 J/m<sup>2</sup> with S.D. of 0.9 J/m<sup>2</sup> and that using Flare<sup>TM</sup> is 18 J/m<sup>2</sup> with S.D. of 2.2 J/m<sup>2</sup>).

본딩 후에는 거의 변하지 않았다. 그러나, BCB를 이용해 본딩된 웨이퍼들에서 EBR 영역은 웨이퍼 본딩 후에는 거의 없어지는 데 이는 BCB의 interlocking action이 본딩 공정 동안 EBR 영역을 채웠기 때문이다[12](Fig. 6c와 6d 비교).

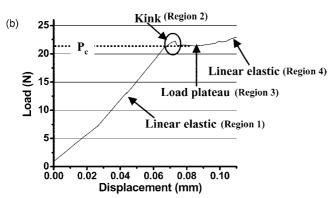

#### 3-4. Flare와 BCB의 본딩 결합력 비교

BCB와 Flare를 이용하여 본딩 된 웨이퍼들은 본딩 면적은 넓고 면도날에 의한 정성적인 본딩 결합력 시험에서는 박리 되지 않을 정도의 충분히 높은 본딩 결합력을 가지고 있다. 상기 두가지 접착 물질들의 박리 가능성을 평가하기 위해, 이들 접착 물질을 이용하 여 본딩된 웨이퍼들의 본딩 결합력의 정량적인 측정을 시도하였다. 이러한 본딩 결합력의 정량적 평가를 위해 4-점 굽힘시험을 이용하 였다. Fig. 7은 BCB와 Flare를 이용해 본딩된 웨이퍼 구조 및본딩 결합력 결과를 보여준다. 이때 사용된 BCB와 Flare 두께는 각각 2.6, 0.6 μm이다. BCB의 경우에는 본딩 결합력를 개선하기 위해 본딩 촉진제를 시용하였다. 이러한 본딩 촉진제의 사용를 사용함에 따라 증가되는 본딩 결합력은 본딩 촉진제와 BCB 레진 및 웨이퍼 사이 의 화학반응에 기인한다. BCB와 Flare 두 물질에서 약한 계면은 모 두 유리 웨이퍼와 접착 물질 사이이다. 이러한 시험 결과, 비록 Flare 의 두께가 BCB 두께보다 얇지만, Flare와 유리 웨이퍼 사이의 계면 에서 본딩 결합력은 18 J/m²이고 BCB와 유리 웨이퍼 사이의 계면 에서 본딩 결합력은 9 J/m<sup>2</sup>으로 측정되었다.

Flare의 히드록실(hydroxyl) 기는 유리 웨이퍼의 실라놀 기와 실리콘 웨이퍼의 자연 산화층과 반응하여 강한 본딩 결합력을 갖는 실록산 결합을 형성한다. BCB의 경우는 사일렌(silane)을 기본 구조로 하는 본딩 촉진제의 4개의 반응기 중, 3개의 아세톡시(acetoxy,

OCOCH<sub>3</sub>) 기는 글래스 웨이퍼와 실리콘 웨이퍼의 자연 산화층의 매달린 실라놀기와 실록산 본드를 형성하고, 1개의 비닐기(vinyl, CH<sub>2</sub>CH)는 BCB 레진의 비닐기와 공유 결합을 통한 강한 화학적 본 딩을 형성한다[15]. Flare에서의 반응 그룹들의 밀도는 BCB보다 높고, 이러한 밀도의 차이가 본딩 결합력에서의 차이를 초래하는 것으로 생각된다.

그러나 이러한 BCB와 유리 웨이퍼 사이 계면의 본딩 결합력은, BEOL 전기 배선 구조인 구리와 다공질 저유전체 사의의 계면의 본딩 결합력(6 J/m²) 보다 높고, BCB 본딩 후, 후속 연삭, 연마 및 CMP 공정에서 본딩 계면이 박리 되지 않았으므로[11], BCB와 글래스 웨이퍼 사이 계면의 본딩 안정성은 여전히 우수하다고 평가할 수 있다. 본딩된 영역의 측면에서, BCB를 이용하여 본딩한 웨이퍼의 본딩 영역이 Flare를 이용한 것 보다 더 넓게 확보되고 그 결과가 재현성 있게 얻어지므로, 본 연구에서는 BCB가 표준 본딩용고분자 수지로 가장 적절하다고 판단하였다.

### 4. 결 론

저유전체 고분자 수지를 이용한 웨이퍼 본딩은 웨이퍼 레벨 3차 원 회로 집적을 구현하기위한 주된 공정이다. 본 연구에서는 이러 한 고분자 수지를 이용하면서 기존의 BEOL 공정과 조화 될 수 있 는 200 mm 웨이퍼 본딩 및 3차원 비아 고리 테스트 구조를 제안 하였다. 다른 고분자 수지와 비교했을때, BCB나 Flare 수지를 이용 하여 본딩된 웨이퍼 들에서 박층화 공정 후에도 박리되지 않고 좋 은 본딩 안정성을 유지하는 결과를 얻을 수 있었다. 본딩 결합력을 정량적으로 측정하기 위한 4-점 굽힘시험 방법을 통해, BCB와 유 리 웨이퍼 사이의 계면에서는 9 J/m<sup>2</sup>의 본딩 결합력이, Flare와 유 리 웨이퍼 사이의 계면에서는 18 J/m<sup>2</sup>의 본딩 결합력이 측정되었다. 비록 BCB를 이용해 본딩된 웨이퍼들의 본딩 결합력이 Flare를 이 용한 것보다는 낮지만, 이 값은 여전히 구리와 다공질 저유전체 사 이 계면의 본딩 결합력(6 J/m²)보다 높고, 본딩된 영역이 재현성있 게 거의 100%에 가깝게 얻어지므로, 본 연구에서는 BCB가 웨이퍼 레벨 3차원 회로 집적을 위한 웨이퍼 본딩 공정의 표준 본딩용 고 분자 수지로 가장 적절하다고 판단하였다.

#### 감 사

이 논문을 미국 렌슬리어의 Interconnect Focus Center 를 통해 지원해 준 DARPA, MARCO 그리고 NYSTAR 담당자에게 감사 드립니다.

#### 참고문헌

- 1. *International Technology Roadmap for Semiconductors (ITRS)*: 2003 Edition(Semiaconductor Industry Association, 2003).

- Davis, J. A., Venkatesan, R., Kaloyeros, A., Beylansky, M., Souri, S. J., Banerjee, K., Saraswat, K. C., Rahman, A., Reif, R. and Meindl, J. D., "Interconnect Limits on Gigascale Integration (GSI) in the 21<sup>st</sup> Century," *Proc. IEEE*, 89(3), 305-324(2001).

- 3. Lu, J.-Q., Kwon, Y., Rajagopalan, G., Gupta, M., McMahon, J., Lee, K.-W., Kraft, R. P., Jindal, A., McDonald, J. F., Cale, T. S., Gutmann, R. J., Xu, B., Eisenbraun, E., Castracane, J. and Kaloyeros,

- A., "A Wafer-Scale 3D IC Technology Platform using Dielectric Bonding Glues and Copper Damascene Patterned Inter-Wafer Interconnects," 2002 IEEE Int'l Interconnect Technol. Conf., 78-80(2002).

- Guarini, K. W., Topol, A. W., Ieong, M., Yu, R., Shi, L., Newport, M. R., Frank, D. J., Singh, D. V., Cohen, G. M., Nitta, S. V., Boyd, D. C., O'Neil, P. A., Tempest, S. L., Pogge, H. B., Purushothaman, S. and Haensch, W. E., "Electrical Integrity of State-Of-The-Art 0.13 um SOI CMOS Devices and Circuits Transferred for 3D IC Fabrication," *Dig. Int'l Elect. Dev. Meeting*, 943-945(2002).

- Rahman, A., Fan, A., Chung, J. and Reif, R., "Comparison of Key Performance Metrics in Two- and Three-Dimensional Integrated Circuits," 2000 IEEE Int'l Interconnect Technol. Conf., 18-20(2000).

- Souri, S. J. and Saraswat, K. C., "Interconnect Performance Modeling for 3D Integrated Circuits with Multiple Si Layers," 1999 IEEE Int'l Interconnect Technol. Conf., 24-26(1999).

- Lee, K. W., Nakamura, T., Ono, T., Yamada, Y., Mizukusa, T., Park, K. T., Kurino, H. and Koyanagi, M., "Three-Dimensional Shared Memory Fabricated using Wafer Stacking Technology," *Dig. Int'l Elect. Dev. Meeting*, 165-167(2000).

- 8. Kwon, Y., "Wafer Bonding for 3D Integration," *Ph.D. Thesis*, Rensselaer Polytechnic Institute, Troy, NY (2003).

- Kwon, Y., Jindal, A., McMahon, J. J., Lu, J.-Q., Gutmann, R. J. and Cale, T. S., "Dielectric Glue Wafer Bonding for 3D Ics," *Mater. Res. Soc. Symp. Proc.*, 766, 27-32(2003).

- Lu, J.-Q., Kwon, Y., Kraft, R. P., Gutmann, R. J., McDonald, J. F. and Cale, T. S., "Stacked Chip-to-Chip Interconnections using Wafer Bonding Technology with Dielectric Bonding Glues," 2001 IEEE Int'l Interconnect Technol. Conf., 219-221(2001).

- 11. Kwon, Y., Seok, J., Lu, J.-Q., Cale, T. S. and Gutmann, R. J.,

- "Thermal Cycling Effects on Critical Adhesion Energy and Residual Stress in Benzocyclobutene-Bonded Wafers," *J. Electrochem. Soc.*, **152**(4), G286-G294(2005).

- Kwon, Y., Lu, J.-Q., Kraft, R. P., Gutmann, R. J., McDonald, J. F. and Cale, T. S., "Wafer Bonding using Dielectric Polymer Thin Films in 3D Integration," *Mater. Res. Soc. Symp. Proc.*, 710, 231-236(2002).

- 13. De Gennes, P. G., "Reptation of a Polymer Chain in The Presence of Fixed Obstacles," J. Chem. Phys., **55**(4), 572-579(1971).

- Sperling, L. H., "Introduction to Physical Polymer Science," Wiley Interscience (1997).

- Snodgrass, J. M., Pantelidis, D., Jenkins, M. L., Bravman, J. C., and Dauskardt, R. H., "Subcritical Debonding of Polymer/Silica Interfaces under Monotonic and Cyclic Loading," *Acta Metall.*, 50(9), 2395-2411(2002).

- Charalambides, P. G., Lund, J., Evans, A. G. and McMeeking, R. M., "A Test Specimen for Determining the Fracture Resistance of Bimaterial Interfaces," J. Appl. Mech., 56(1), 77-82(1989).

- Chua, C. T., Sarkar, G. and Hu, X., "In Situ Characterization of Methylsilsesquioxane Curing," *J. Electrochem. Soc.*, **145**(11), 4007-4011(1998).

- Vrtis, R. N., Heap, K. A., Burgoyne, W. F. and Robeson, L. M., "Poly(Arylene Ethers) as Low Dielectric Constant Materials for ULSI Interconnect Applications," *Mater. Res. Soc. Symp. Proc.*, 443, 171-176(1997).

- Garrou, P. E., Heistand, R. H., Dibbs, M. G., Mainal, T. A., Mohler, C. E., Stokich, T. M., Townsend, P. H., Adema, G. M., Berry, M. J. and Turlik, I., "Rapid Thermal Curing of BCB Dielectric," *IEEE Trans. Comp., Hybrids Manufact. Technol.*, 16(1), 46-52(1993).